CYBERNET SYSTEMS CO., LTD.

# **IBIS Model Engineering for SI Simulation**

#### Asian IBIS Summit (CHINA), October 27, 2006

Kazuhiko Kusunoki k-kusu@cybernet.co.jp

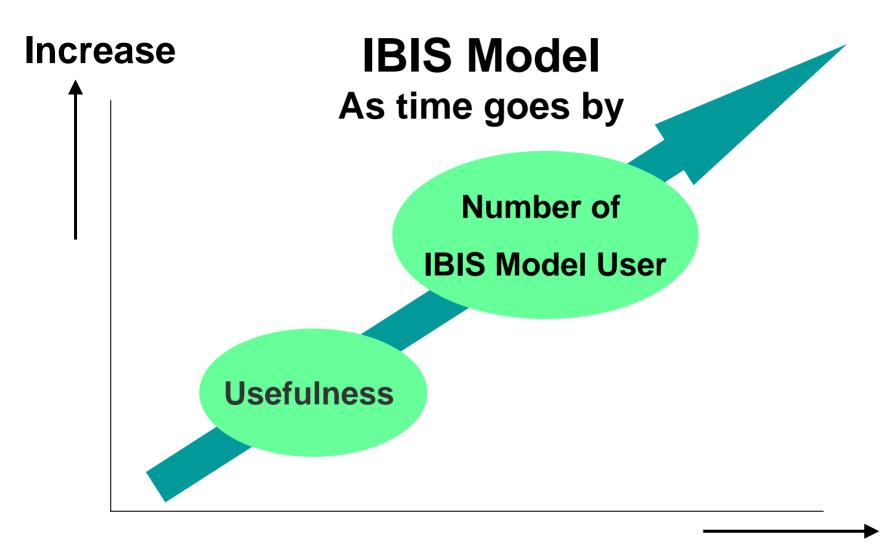

# **IBIS model goes mainstream**

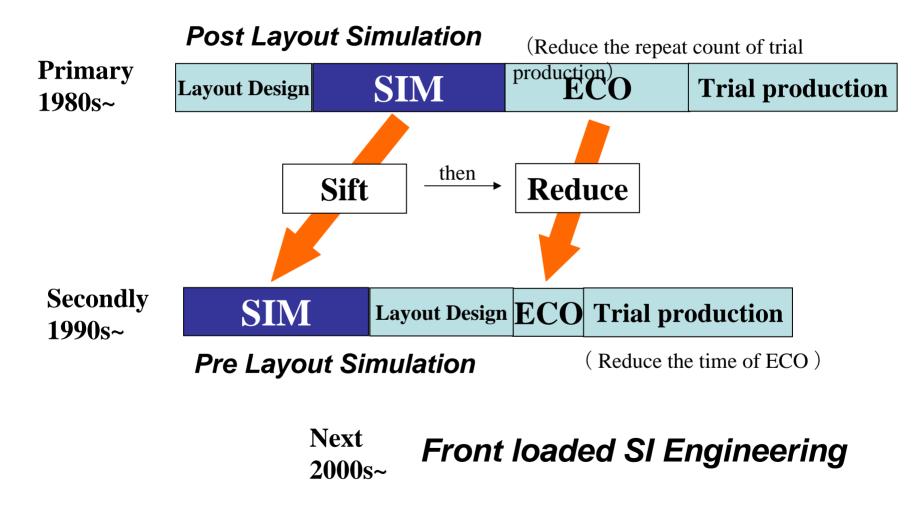

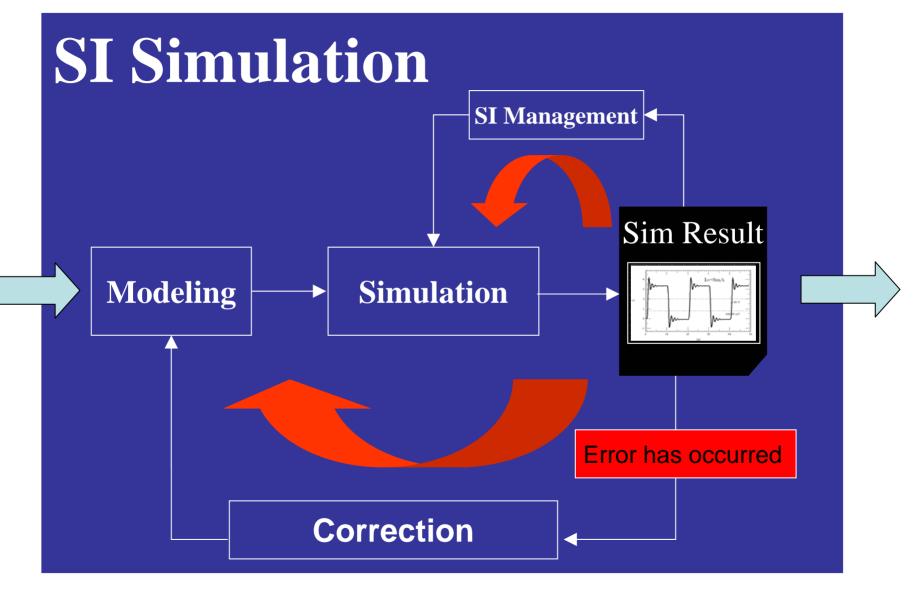

**Challenge to the SI simulation Engineering of PCB Design**

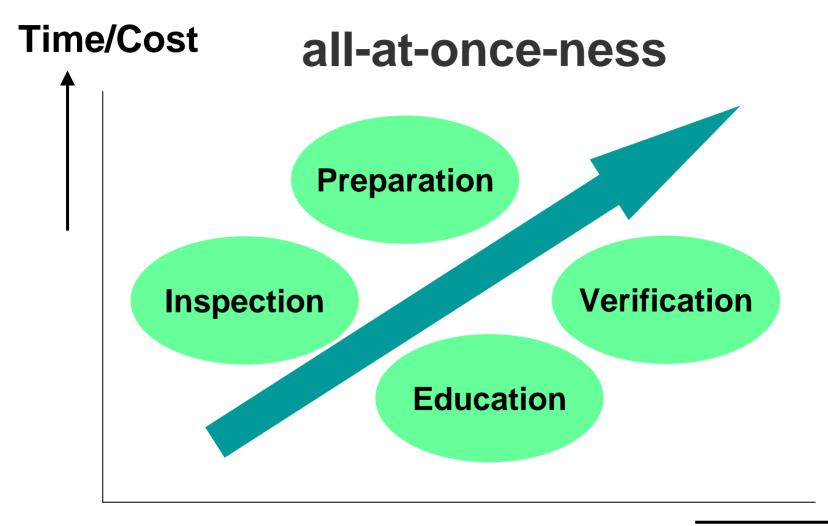

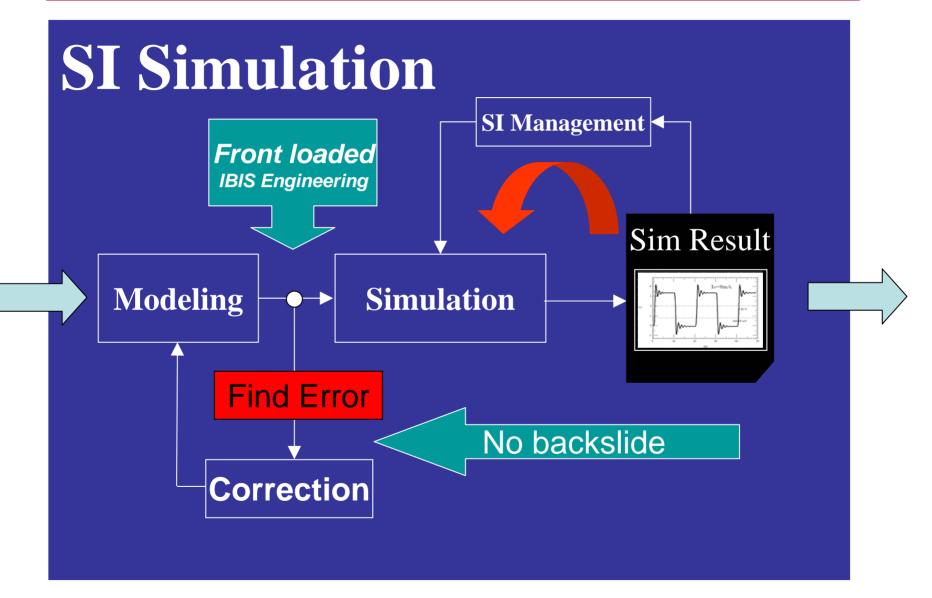

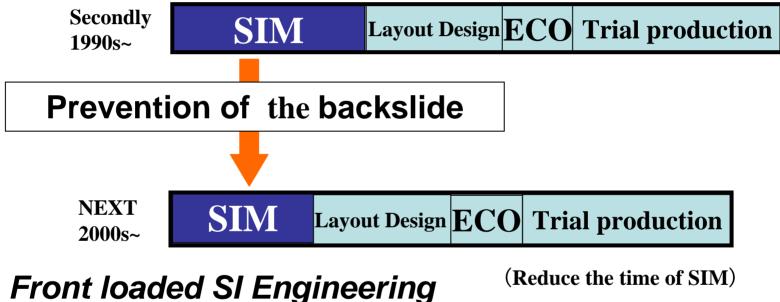

# IBIS model Engineering as Front loaded SI Engineering To minimized the time of SI simulation

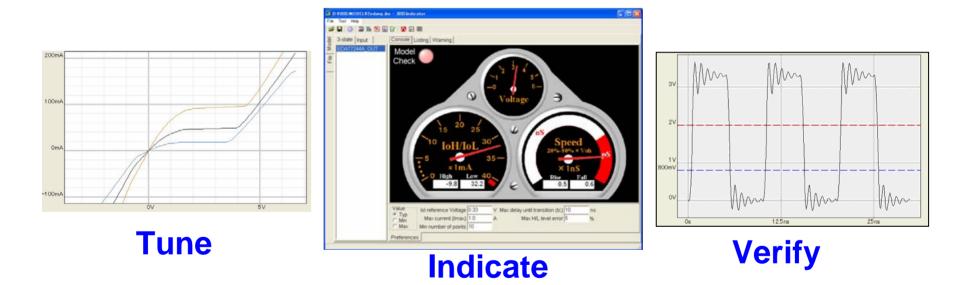

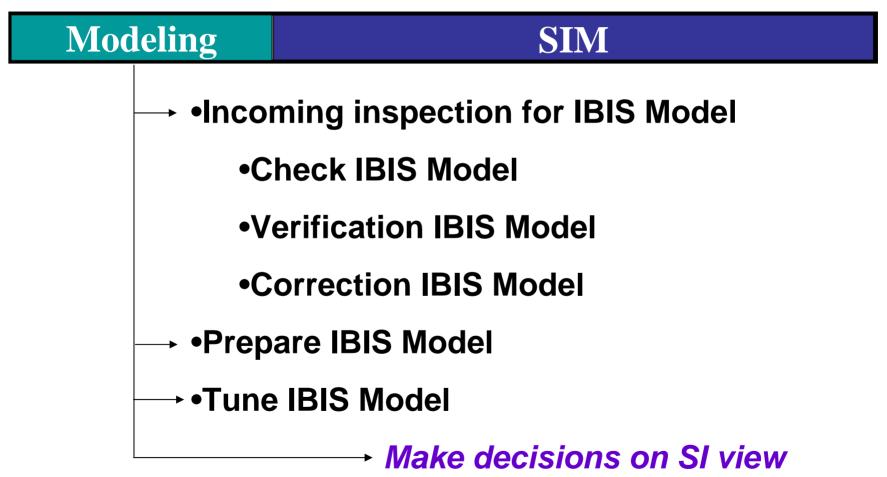

# **Incoming inspection for IBIS Model**

#### •Syntax Check

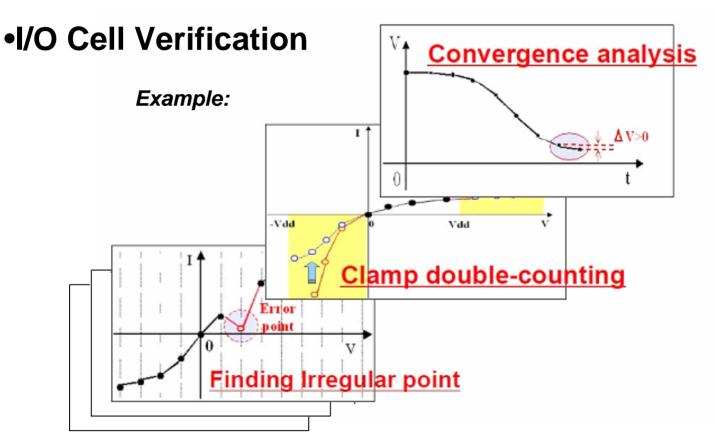

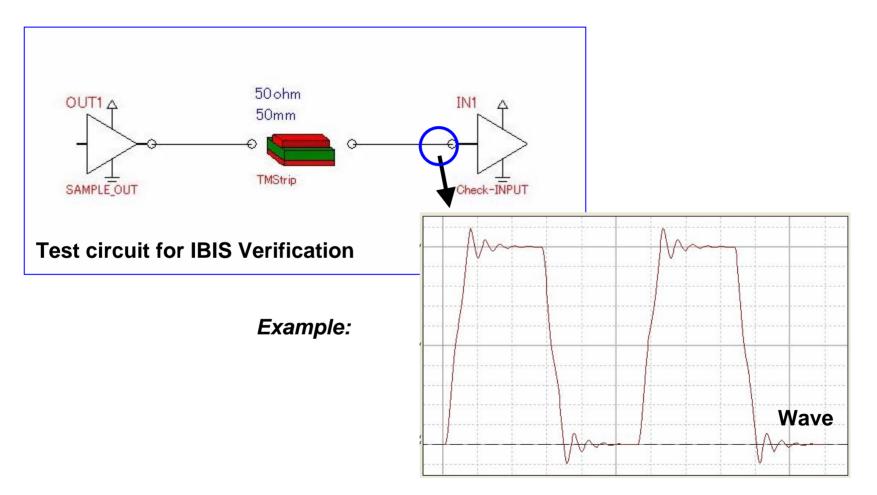

# •Verification IBIS Model

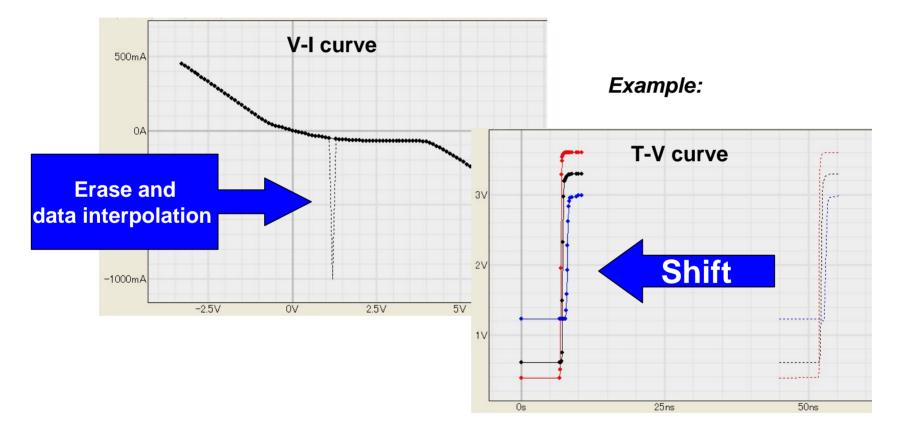

# Correction IBIS Model

#### •Prepare IBIS Model

#### Pin/Signal/Model Assign

|                                                                                                                | 5      | 5             |     |     |            |          |      |     |            |            |            | 000 | i no     | in a                                                 |          |   |

|----------------------------------------------------------------------------------------------------------------|--------|---------------|-----|-----|------------|----------|------|-----|------------|------------|------------|-----|----------|------------------------------------------------------|----------|---|

| Pin#                                                                                                           | Signal | Model         | Rpi | n   |            |          | Lpin | n   | 007        |            |            |     |          | $) \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ |          |   |

| A001                                                                                                           | 1-     |               |     |     |            |          |      |     | 009        |            |            | 000 |          |                                                      |          |   |

| A002                                                                                                           |        | EDA77244A_IN  |     |     |            |          |      |     | 010        |            | • •        |     |          |                                                      |          |   |

| A003                                                                                                           | 1.     | EDA77244A_IN  |     |     |            |          | 1    |     | 011        |            |            |     |          |                                                      |          |   |

| A004                                                                                                           | 12     | EDA77244A IN  |     |     |            |          |      | _   | 012        |            |            |     |          |                                                      |          |   |

| A005                                                                                                           | -      | EDA77244A IN  |     |     |            |          |      | _   | 014        |            |            |     |          | •••                                                  |          |   |

| A006                                                                                                           |        | EDA77244A_IN  |     |     |            |          |      |     | 015        |            |            |     |          |                                                      |          | - |

| A007                                                                                                           |        | EDA77244A IN  |     |     |            |          | 1    |     | A          | ч в с      | DE         | FG  | i H J    | κι                                                   | MN       | Ρ |

| A008                                                                                                           |        | GND -         |     |     |            |          |      |     |            |            |            |     |          |                                                      |          |   |

| A009                                                                                                           |        | POWER         |     | 1   | 2          | 3        | 4    | 5   | 6          | 7          | 8          | 9   | 10       | 11                                                   | 12       | 1 |

| A010                                                                                                           |        | NC            | A   | 1   | 44         | 43       | 42   | 41  | 40         | 30         | 38         | 37  | 36       | 35                                                   | 34       | 1 |

| A011                                                                                                           | 5-     | EDA77244A_OUT | B   | 2   | 45         | 80       | 70   | 78  | 77         | 76         | 75         | 74  | 73       | 72                                                   | 33       |   |

| A012                                                                                                           | 19     | EDA77244A OUT |     | 3   | 4 î<br>4 7 | 81<br>82 | 108  | 107 | 106        | 105<br>126 | 104<br>125 | 103 | 102      | 71<br>70                                             | 32<br>31 | - |

| A013                                                                                                           |        | EDA77244A_OUT | E   | 5   | 48         | 83       | 110  | 129 | 140        | 139        | 138        | 123 | 100      | 69                                                   | 30       |   |

| A014                                                                                                           |        | EDA77244A_OUT | F   | 6   | 49         | 84       | 111  | 130 | 141        | 144        | 137        | 122 | 99       | 68                                                   | 29       |   |

| A015                                                                                                           |        | EDA77244A_OUT | G   | 7   | 50         | 85       | 112  | 131 | 142        | 143        | 136        | 121 | 98       | 67                                                   | 28       |   |

| B001                                                                                                           |        | EDA77244A_OUT | H   | 8   | 5<br>52    | 86<br>87 | 113  | 132 | 133<br>116 | 134        | 135<br>118 | 120 | 97<br>96 | 66<br>65                                             | 27<br>26 | 4 |

| B002                                                                                                           |        | CON7244H_001  | Г К | 10  | 58         | 88       | 89   | 90  | 91         | 92         | 93         | 94  | 95       | 64                                                   | 25       |   |

| the second s |        |               | L   | 11, | 54         | 55       | 56   | 57  | 58         | 59         | 60         | 01  | 02       | 63                                                   | 24       |   |

| B003                                                                                                           |        |               | M   | 12  | 13         | 14       | 15   | 16  | 17         | 18         | 19         | 20  | 21       | 22                                                   | 23       |   |

|                                                                                                                |        |               |     |     |            |          |      |     |            |            |            |     |          |                                                      |          |   |

# **Spiral pin number location**

A B C D E F G H J K L M N P Q **BGA**

P Q

#### Comparison-data for the best result

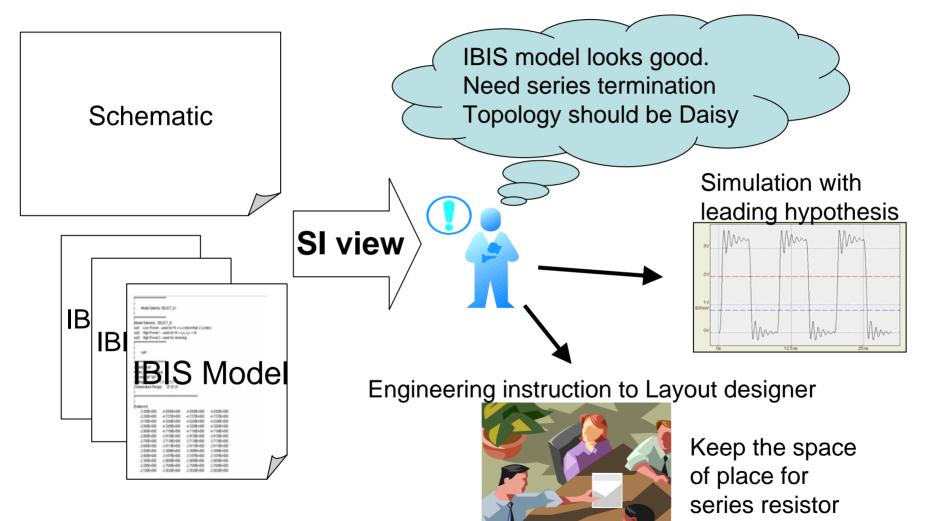

# What the SI Electronics whiz does for IBIS?

in advance

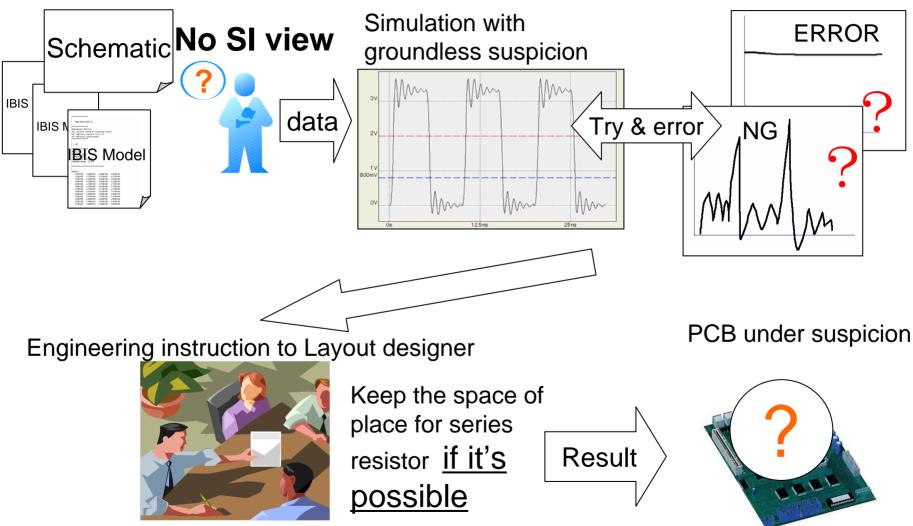

# What the Non SI Electronics whiz may do?

#### IBIS model Engineering as Front loaded SI Engineering

| <b>IBIS Mode</b>   |                   |               |         |

|--------------------|-------------------|---------------|---------|

| ****               | *****             |               |         |

| [Model] A          |                   |               |         |

| Model_type I/O     |                   |               |         |

| Polarity Non-I     | nverting          |               |         |

| Enable Activ       | e-Low             |               |         |

| Vinl = 0.66V       |                   |               |         |

| Vinh = 2.00V       |                   |               |         |

| C_comp 2.55pF 1.   | 18pF 3.91pF       |               |         |

| [Voltage Range] 3. | 3V 3.0V 3.6V      |               |         |

| [Power Clamp Ref   | erence] 3.3V 3.0  | V 3.6V        |         |

| [GND Clamp Refe    | rence] 0.0V 0.0V  | 7 <b>0.0V</b> |         |

| [Pullup Reference] | 3.3V 3.0V 3.6V    |               |         |

| [Pulldown Referen  | ce] 0.0V 0.0V 0.  | 0V            |         |

| [Temperature Ran   | ge] 49.0 125.0 -2 | 20.0          |         |

|                    |                   |               |         |

| ****               | *****             | *****         | ******  |

|                    |                   |               |         |

| [Pulldown]         |                   |               |         |

| -3.300E+00         | -2.7539E-01       | -2.2720E-01   | -3.4332 |

| -3.200E+00         | -2.6889E-01       | -2.2122E-01   | -3.3549 |

| -3.100E+00         | -2.6192E-01       | -2.1499E-01   | -3.2720 |

|                    |                   |               |         |

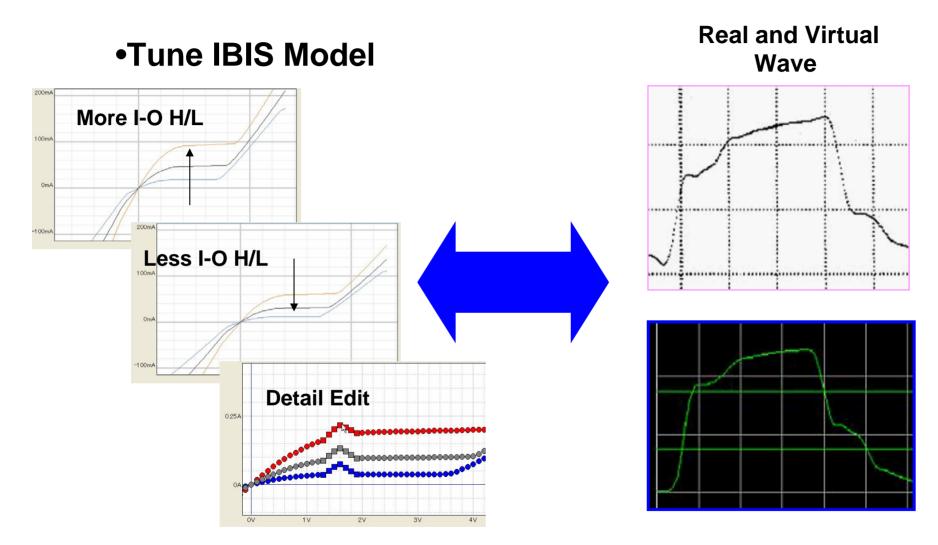

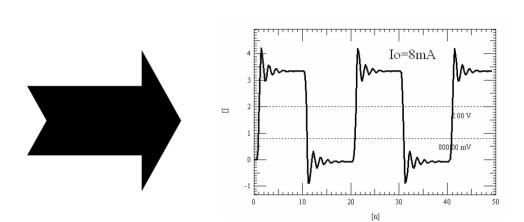

# Predict Signal Wave from IBIS Model

# *IBIS model Engineering as Front loaded SI Engineering*

- Take a look (evaluate a symptom) of Output Current

- Take a look (evaluate a symptom) of Rise/Fall Speed

- Take a look (evaluate a symptom) of Signal amplitude

- Trend prediction for Routing Topology, Cross Talk ,etc

| Procurement | Verification | Correction | Make decisions |

|-------------|--------------|------------|----------------|

| IBIS model  | IBIS model   | IBIS model | on SI view     |

|             |              |            |                |

# To minimized the time of SI simulation

#### **Pre Layout Simulation**

As far in advance as possible

#### CYBERNET SYSTEMS CO., LTD.

# **IBIS model goes mainstream**

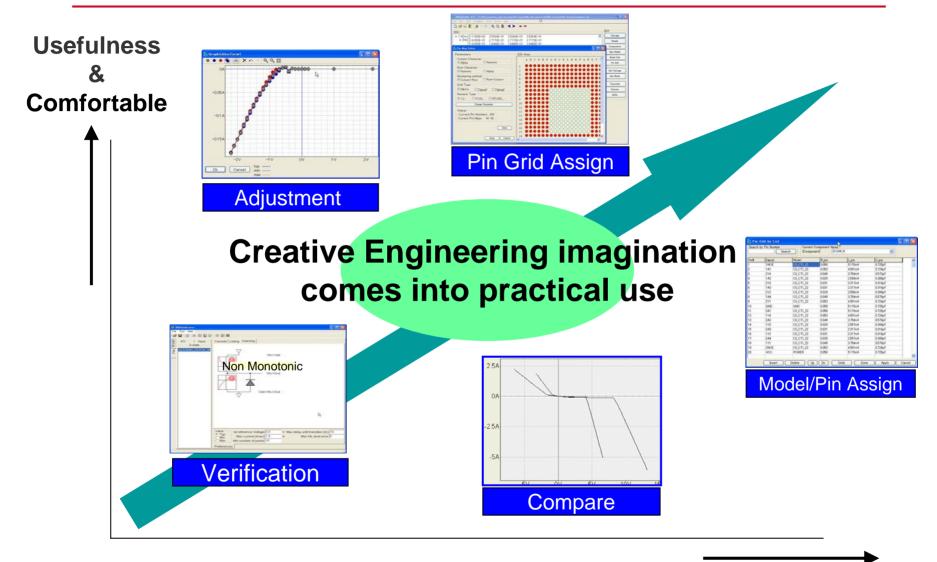

# Make IBIS more comfortable 使IBIS使用更方便